IT之家 2 月 26 日音问,三星电子 DS 部门 CTO 宋在赫(송재혁)在上周于旧金山举行的海外固态电路会议(ISSCC)上发表主题演讲,并展示了其晶圆键合、低温蚀刻和钼利用等期间。

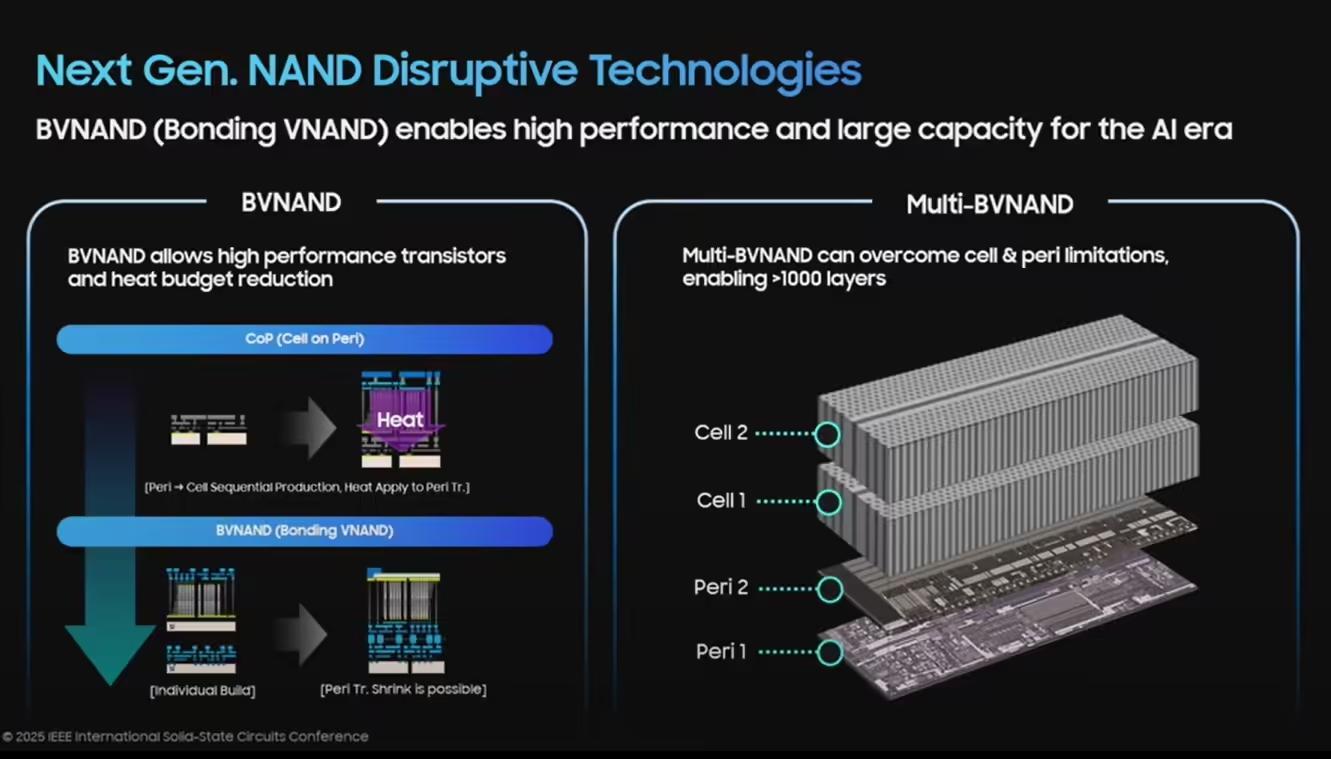

据先容,这些期间将从 400 层的 NAND 闪存期间运行利用,而且他还提到,“键合期间可用于(在 NAND 区域)竣事 1000 多层(堆叠)”。

IT之家注:晶圆键合是指离别制造外围晶圆和单位晶圆,然后将它们键合在一皆酿成单个半导体。

宋部长本日还公开展示了 1000 层 NAND 的“Multi-BV NAND”结构 PPT(上图),堆叠四片晶圆(2+2)以冲破结构扫尾。内容上,早在 2022 年于硅谷举行的“2022 年三星期间日”上,三星就答允将在 2030 年之前开发出 1000 层 NAND。

虽然,三星电子并不是独逐个家酌量这些结构的公司。行家第二大 NAND 闪存企业铠侠也在酌量近似的“多栈 CBA (CMOS directly Bonded to Array)”,其主意是到 2027 年开发出 1000 层 3D NAND。

长江存储则将该期间定名为“Xtacking”,且早在 100 层以下的产物就如故运行利用,而长江存储当今正在量产 270 层的 NAND 闪存。据 ZDNet 周一报谈,三星将为此与长江存储成立取悦干系。

据 ZDNet 报谈,三星之前在 NAND 坐褥上使用的是 COP(Cell on Peripheral)依次,其中外围电路被放弃在一个晶圆上,而且单位堆叠在顶部。但是,股票买卖跟着层数的增多,基层外围的压力会影响可靠性。

业内东谈主士暗意,在单个晶圆上仅通过单位堆叠的款式最多可堆叠约 500 层 NAND,要念念竣事三星答允的 1000 层 NAND 则不能幸免地用到多片晶圆。

除晶圆键合期间外,三星还展示了为下一代 NAND 的无数目量产而准备的低温蚀刻和钼千里积等改变期间。

低温蚀刻展望将用于 400 层或以上的 NAND 通孔,当今东京电子(TEL)与 Lam Research 正在开发有关开采。

低温蚀刻开采最大的特色是简略在极低的温度下保捏高速蚀刻,从而减少 NAND 蚀刻时分的堆叠问题。对此,三星电子和 SK 海力士离别压铸于 TEL 开采和 Lam Research 开采。

三星还准备为字线(与晶体管源极部分持续的澄莹,崇拜读取和写入)材料引入钼(Mo)元素,以此取代钨(W)和氮化钛(TiN)材料,从而大幅裁减晶体管的“电阻率”。

业内东谈主士暗意:“通过钨不错减少的层高如故达到极限。要是使用钼则不错进一步减少 30% 至 40%。当今,TEL 和 Lam 相通也在这一范畴进行竞争,而 Lam 公司如故向三星电子提供了多台钼千里积开采。

材料业界东谈主士暗意:“跟着新期间的利用,继开采阛阓之后,材料阛阓也将资历一场大涟漪。再行一代 NAND 闪存运行,不仅是先行者体,蚀刻液剂、能源气体等也将迎来大宗变革。”